# Bruce Dang, Alexandre Gazet, and Elias Bachaalany

with contributions from Sébastien Josse

# PRACTICAL REVERSE ENGINEERING

X86, X64, ARM, WINDOWS® KERNEL, REVERSING TOOLS, AND OBFUSCATION

# **Practical Reverse Engineering**

# Practical Reverse Engineering

x86, x64, ARM, Windows® Kernel, Reversing Tools, and Obfuscation

Bruce Dang Alexandre Gazet Elias Bachaalany

with contributions from Sébastien Josse

WILEY

### Practical Reverse Engineering: x86, x64, ARM, Windows® Kernel, Reversing Tools, and Obfuscation

Published by John Wiley & Sons, Inc. 10475 Crosspoint Boulevard Indianapolis, IN 46256 www.wiley.com

Copyright © 2014 by Bruce Dang Published by John Wiley & Sons, Inc., Indianapolis, Indiana Published simultaneously in Canada

ISBN: 978-1-118-78731-1 ISBN: 978-1-118-78725-0 (ebk) ISBN: 978-1-118-78739-7 (ebk)

Manufactured in the United States of America

10987654321

No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except as permitted under Sections 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 646-8600. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, (201) 748-6011, fax (201) 748-6008, or online at http://www.wiley.com/go/permissions.

Limit of Liability/Disclaimer of Warranty: The publisher and the author make no representations or warranties with respect to the accuracy or completeness of the contents of this work and specifically disclaim all warranties, including without limitation warranties of fitness for a particular purpose. No warranty may be created or extended by sales or promotional materials. The advice and strategies contained herein may not be suitable for every situation. This work is sold with the understanding that the publisher is not engaged in rendering legal, accounting, or other professional services. If professional assistance is required, the services of a competent professional person should be sought. Neither the publisher nor the author shall be liable for damages arising herefrom. The fact that an organization or Web site is referred to in this work as a citation and/or a potential source of further information does not mean that the author or the publisher endorses the information the organization or website may provide or recommendations it may make. Further, readers should be aware that Internet websites listed in this work may have changed or disappeared between when this work was written and when it is read.

For general information on our other products and services please contact our Customer Care Department within the United States at (877) 762-2974, outside the United States at (317) 572-3993 or fax (317) 572-4002.

Wiley publishes in a variety of print and electronic formats and by print-on-demand. Some material included with standard print versions of this book may not be included in e-books or in print-on-demand. If this book refers to media such as a CD or DVD that is not included in the version you purchased, you may download this material at http://booksupport.wiley.com. For more information about Wiley products, visit www.wiley.com.

### Library of Congress Control Number: 2013954099

**Trademarks:** Wiley and the Wiley logo are trademarks or registered trademarks of John Wiley & Sons, Inc. and/or its affiliates, in the United States and other countries, and may not be used without written permission. All other trademarks are the property of their respective owners. John Wiley & Sons, Inc. is not associated with any product or vendor mentioned in this book.

| This book is dedicated to those who relentlessly pursue knowledge and selflessly share it with others. |

|--------------------------------------------------------------------------------------------------------|

|                                                                                                        |

|                                                                                                        |

|                                                                                                        |

|                                                                                                        |

# **About the Authors**

Bruce Dang is a senior security development engineering lead at Microsoft working on security technologies in unreleased Microsoft products. Previously, he worked on security vulnerabilities reported to Microsoft and was the first to publicly share analytical techniques for targeted attacks with Office documents. He and his team analyzed the famous Stuxnet malware, which supposedly attacked the Iranian uranium enrichment process. He has spoken at RSA, BlackHat Vegas, BlackHat Tokyo, Chaos Computer Club, REcon, and many other industry conferences.

**Alexandre Gazet** is a security researcher at Quarkslab. His interests focus on reverse engineering, software protections, and vulnerability research. Alexandre has presented at several conferences, including HITB Kuala Lumpur (2009) and REcon Montreal (2010 and 2011).

Elias Bachaalany has been a computer programmer, reverse engineer, freelance technical writer, and an occasional reverse engineering trainer for the past 14 years. Over his long career, Elias has worked with various technologies, including writing scripts, doing extensive web development, working with database design and programming, writing device drivers and low-level code such as boot loaders or minimal operating systems, writing managed code, assessing software protections, and writing reverse engineering and desktop security tools. Elias has also presented twice at REcon Montreal (2012 and 2013).

While working for Hex-Rays SA in Belgium, Elias helped to improve and add new features to IDA Pro. During that period, he authored various technical blog posts, provided IDA Pro training, developed various debugger plugins, amped up IDA Pro's scripting facilities, and contributed to the IDAPython project since version 1.2.0 and onwards. Elias currently works at Microsoft with a talented team of software security engineers.

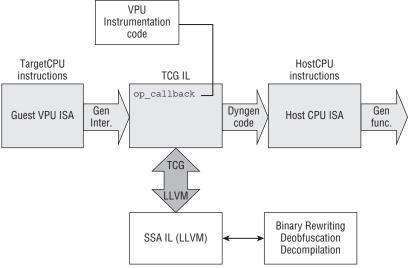

**Sébastien Josse** is a security researcher at the French Ministry of Defense (Direction Générale de l'Armement). He has more than ten years of experience as an instructor, researcher, and consultant in the field of information systems security, in both the civilian and defense sectors. He dedicated his PhD dissertation (École Polytechnique, 2009) to the dynamic analysis of protected programs, focusing mainly on cryptographic mechanisms resistant to reverse engineering and on the use of a virtualization system to carry through analysis of protected programs. He has published in the journal *JICV* and several conferences proceedings, including ECRYPT (2004), EICAR (2006, 2008, 2011), AVAR (2007) and HICSS (2012, 2013 and 2014).

# **About the Technical Editor**

Matt Miller is a principal security engineer in Microsoft's Trustworthy Computing organization, where he currently focuses on researching and developing exploit-mitigation technology. Prior to joining Microsoft, Matt was core developer for the Metasploit framework and a contributor to the journal *Uninformed*, where he wrote about topics related to exploitation, reverse engineering, program analysis, and operating system internals.

# **Credits**

**Executive Editor** Carol Long

**Project Editor**John Sleeva

**Technical Editor** Matt Miller

**Production Editor**Daniel Scribner

Copy Editor Luann Rouff

**Editorial Manager** Mary Beth Wakefield

Freelancer Editorial Manager

Rosemarie Graham

**Associate Director of**

**Marketing**David Mayhew

Marketing Manager Ashley Zurcher

**Business Manager**

Amy Knies

Vice President and Executive

**Group Publisher** Richard Swadley

**Associate Publisher**

Jim Minatel

Project Coordinator, Cover

Todd Klemme

Proofreader

Josh Chase, Word One New York

**Indexer** Ron Strauss

**Cover Designer** Ryan Sneed

# **Acknowledgments**

Writing this book has been one of the most interesting and time-consuming endeavors we have ever gone through. The book represents something that we wish we had when we started learning about reverse engineering more than 15 years ago. At the time, there was a dearth of books and online resources (there were no blogs back then); we learned the art primarily through friends and independent trial-and-error experiments. The information security "industry" was also non-existent back then. Today, the world is different. We now have decompilers, web scanners, static source scanners, cloud (?), and APTs (unthinkable!). Numerous blogs, forums, books, and in-person classes aim to teach reverse engineering. These resources vary greatly in quality. Some are sub-standard but shamelessly published or offered to take advantage of the rise in demand for computer security; some are of extremely high quality but not well attended/read due to lack of advertising, specialization or because they are simply "too esoteric." There is not a unifying resource that people can use as the foundation for learning reverse engineering. We hope this book is that foundation.

Now for the best part, acknowledging the people who helped us arrive at where we are today. All of the authors would like to acknowledge Rolf Rolles for his contributions to the obfuscation chapter. Rolf is a real pioneer in the field of reverse engineering. His seminal work on virtual machine deobfuscation, applying program analysis to reverse engineering, and binary analysis education influenced and inspired a new generation of reverse engineers. We hope that he will continue to contribute to the field and inspire others to do the same. Next, we would also like to thank Matt Miller, our comrade and technical reviewer. Matt is another true pioneer in our field and has made seminal contributions to exploit mitigations in Windows. His dedication to details and helping others learn should be a model for all. Finally, we would like to thank Carol Long, John Sleeva, Luann Rouff, and the staff at John Wiley & Sons for putting up with us through the publishing process.

— The authors

I would like to thank my parents for their sacrifices to give me better opportunities in life; my sister and brother, Ivy Dang and Donald Dang, for being a constant source of support and inspiration; and Rolf Rolles for being a good friend and source of reason all these years. I did not have many role models growing up, but the following people directly helped shape my perspectives: Le Thanh Sang, Vint Cerf, and Douglas Comer. At university, I learned the joy of Chinese literature from David Knetchges, Buddhist studies from Kyoko Tokuno, Indian history from Richard Salomon (who would have thought so much can be learned from rocks and coins!), Central Asian history from Daniel Waugh, and Chinese language from Nyan-Ping Bi. While they are not reverse engineers, their enthusiasm and dedication forever inspired and made me a better human being and engineer. If I had met them earlier, my career path would probably be very different.

Through the journey of professional life, I was fortunate enough to meet intelligent people who influenced me (in no particular order): Alex Carp, rebel, Navin Pai, Jonathan Ness, Felix Domke, Karl J., Julien Tinnes, Josh Phillips, Daniel Radu, Maarten Boone, Yoann Guillot, Ivanlef0u (thanks for hosting us), Richard van Eeden, Dan Ho, Andy Renk, Elia Florio, Ilfak Guilfanov, Matt Miller, David Probert, Damian Hasse, Matt Thomlinson, Shawn Hoffman, David Dittrich, Eloi Vanderbeken, LMH, Ali Rahbar, Fermin Serna, Otto Kivling, Damien Aumaitre, Tavis Ormandy, Ali Pezeshk, Gynvael Coldwind, anakata (a rare genius), Richard van Eeden, Noah W., Ken Johnson, Chengyun Yu, Elias Bachaalany, Felix von Leitner, Michal Chmielewski, sectorx, Son Pho Nguyen, Nicolas Pouvesle, Kostya Kortchinsky, Peter Viscerola, Torbjorn L., Gustavo di Scotti, Sergiusz Fonrobert, Peter W., Ilja van Sprundel, Brian Cavenah, upb, Maarten Van Horenbeeck, Robert Hensing, Cristian Craioveanu, Claes Nyberg, Igor Skorchinsky, John Lambert, Mark Wodrich (role model Buddhist), David Midturi, Gavin Thomas, Sebastian Porst, Peter Vel, Kevin Broas, Michael Sandy, Christer Oberg, Mateusz "j00ru" Jurczyk, David Ross, and Raphael Rigo. Jonathan Ness and Damian Hasse were always supportive of me doing things differently and constantly gave me opportunities to fail/succeed. If I forgot you, please forgive me.

The following people directly provided feedback and improved the initial drafts of my chapters: Michal Chmielewski, Shawn Hoffman, Nicolas Pouvesle, Matt Miller, Alex Ionescu, Mark Wodrich, Ben Byer, Felix Domke, Ange Albertini, Igor Skorchinsky, Peter Ferrie, Lien Duong, iZsh, Frank Boldewin, Michael Hale Ligh, Sebastien Renaud, Billy McCourt, Peter Viscerola, Dennis Elser, Thai Duong, Eloi Vanderbeken, Raphael Rigo, Peter Vel, and Bradley Spengler (a true overachiever). Without their insightful comments and suggestions, most of the book would be unreadable. Of course, you can blame me for the remaining mistakes.

There are numerous other unnamed people that contributed to my knowledge and therefore this book.

I also want to thank Molly Reed and Tami Needham from The Omni Group for giving us a license of OmniGraffle to make illustrations in the earlier drafts.

Last but not least, I want to thank Alex, Elias, and Sébastien for helping me with this book. Without them, the book would have never seen the light of day.

— Bruce

First, I would like to thank Bruce Dang for inviting me to take part in this great project. It has been a long and enriching journey. Rolf Rolles was there at first, and I personally thank him for the countless hours we spent together imagining the obfuscation chapter and collecting material. Sébastien Josse then agreed to joined us; his contribution is invaluable and our chapter wouldn't be the same without him. Thank you, Seb.

I also want to thank my friends Fabrice Desclaux, Yoann Guillot, and Jean-Philippe Luyten for their invaluable feedback.

Finally, thanks to Carol Long for making this book possible, and to John Sleeva for keeping us on track.

— Alexandre

I want to start by thanking Bruce Dang, my friend and colleague, for giving me the chance to participate in this endeavor. I also want to thank all my friends and colleagues for their support and help. In particular, I would like to thank Daniel Pistelli (CEO of Cerbero GmbH), Michal Chmielewski, Swamy Shivaganga Nagaraju, and Alexandre Gazet for their technical input and feedback during the writing of the book.

I want to thank Mr. Ilfak Guilfanov (CEO of Hex-Rays SA). I learned a lot from him while working at Hex-Rays. His hard work, patience, and perseverance to create IDA Pro will always be an inspiration to me.

A big thanks to John Wiley & Sons for giving us the opportunity to publish this book. Thanks also to the acquisition editor Carol Long for her prompt and professional assistance, and to the project editor John Sleeva and copy editor Luann Rouff for their energy, patience, and hard work.

— Elias

I want to thank Alexandre, Elias, and Bruce for giving me the opportunity to contribute to this book. I also want to thank Jean-Philippe Luyten for putting us in touch. Finally, thanks to Carol Long and John Sleeva for their help and professionalism in the realization of this project.

— Sébastien

# **Contents at a Glance**

| Introduction | 1                                          | xxiii |

|--------------|--------------------------------------------|-------|

| Chapter 1    | x86 and x64                                | 1     |

| Chapter 2    | ARM                                        | 39    |

| Chapter 3    | The Windows Kernel                         | 87    |

| Chapter 4    | Debugging and Automation                   | 187   |

| Chapter 5    | Obfuscation                                | 267   |

| Appendix     | Sample Names and Corresponding SHA1 Hashes | 341   |

| Index        |                                            | 343   |

# **Contents**

| Introduction | 1                                        | xxiii |

|--------------|------------------------------------------|-------|

| Chapter 1    | x86 and x64                              | 1     |

| -            | Register Set and Data Types              | 2     |

|              | Instruction Set                          | 3     |

|              | Syntax                                   | 4     |

|              | Data Movement                            | 5     |

|              | Exercise                                 | 11    |

|              | Arithmetic Operations                    | 11    |

|              | Stack Operations and Function Invocation | 13    |

|              | Exercises                                | 17    |

|              | Control Flow                             | 17    |

|              | System Mechanism                         | 25    |

|              | Address Translation                      | 26    |

|              | Interrupts and Exceptions                | 27    |

|              | Walk-Through                             | 28    |

|              | Exercises                                | 35    |

|              | x64                                      | 36    |

|              | Register Set and Data Types              | 36    |

|              | Data Movement                            | 36    |

|              | Canonical Address                        | 37    |

|              | Function Invocation                      | 37    |

|              | Exercises                                | 38    |

| Chapter 2    | ARM                                      | 39    |

| -            | Basic Features                           | 40    |

|              | Data Types and Registers                 | 43    |

|              | System-Level Controls and Settings       | 45    |

|              | Introduction to the Instruction Set      | 46    |

|           | Loading and Storing Data             | 47  |

|-----------|--------------------------------------|-----|

|           | LDR and STR                          | 47  |

|           | Other Usage for LDR                  | 51  |

|           | LDM and STM                          | 52  |

|           | PUSH and POP                         | 56  |

|           | Functions and Function Invocation    | 57  |

|           | Arithmetic Operations                | 60  |

|           | Branching and Conditional Execution  | 61  |

|           | Thumb State                          | 64  |

|           | Switch-Case                          | 65  |

|           | Miscellaneous                        | 67  |

|           | Just-in-Time and Self-Modifying Code | 67  |

|           | Synchronization Primitives           | 67  |

|           | System Services and Mechanisms       | 68  |

|           | Instructions                         | 70  |

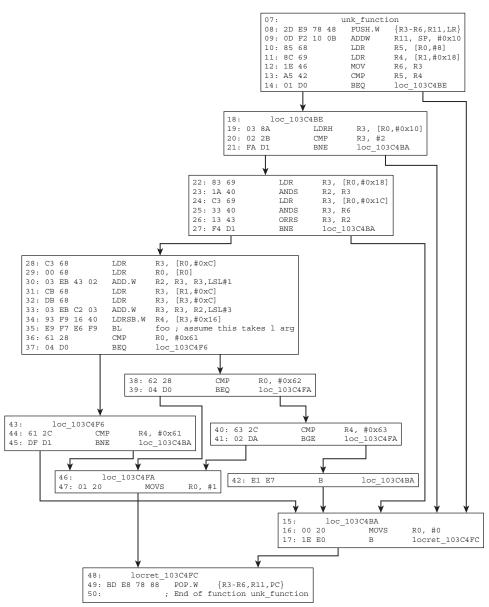

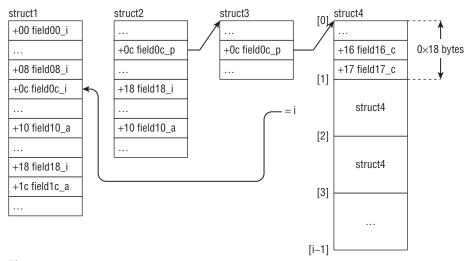

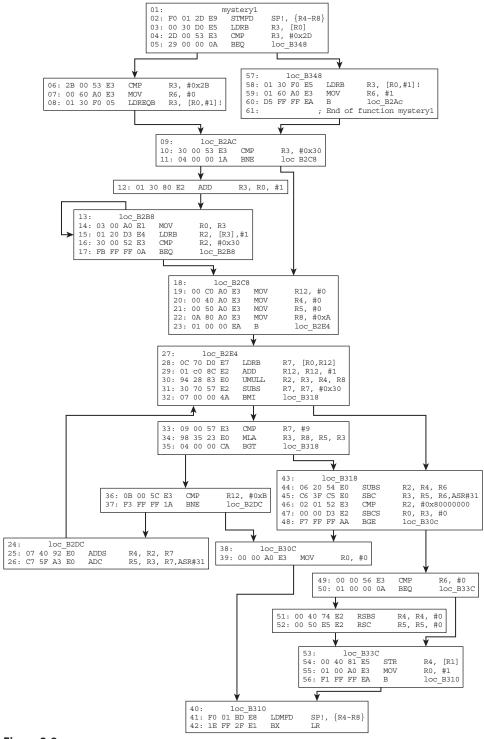

|           | Walk-Through                         | 71  |

|           | Next Steps                           | 77  |

|           | Exercises                            | 78  |

| Chapter 3 | The Windows Kernel                   | 87  |

|           | Windows Fundamentals                 | 88  |

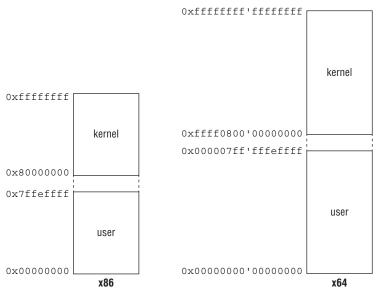

|           | Memory Layout                        | 88  |

|           | Processor Initialization             | 89  |

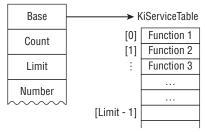

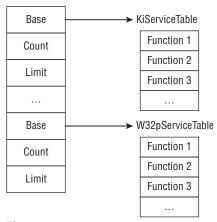

|           | System Calls                         | 92  |

|           | Interrupt Request Level              | 104 |

|           | Pool Memory                          | 106 |

|           | Memory Descriptor Lists              | 106 |

|           | Processes and Threads                | 107 |

|           | Execution Context                    | 109 |

|           | Kernel Synchronization Primitives    | 110 |

|           | Lists                                | 111 |

|           | Implementation Details               | 112 |

|           | Walk-Through                         | 119 |

|           | Exercises                            | 123 |

|           | Asynchronous and Ad-Hoc Execution    | 128 |

|           | System Threads                       | 128 |

|           | Work Items                           | 129 |

|           | Asynchronous Procedure Calls         | 131 |

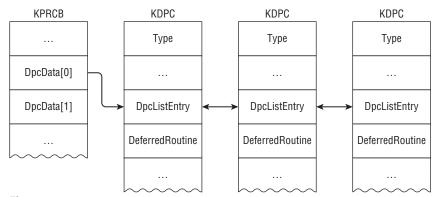

|           | Deferred Procedure Calls             | 135 |

|           | Timers                               | 140 |

|           | Process and Thread Callbacks         | 142 |

|           | Completion Routines                  | 143 |

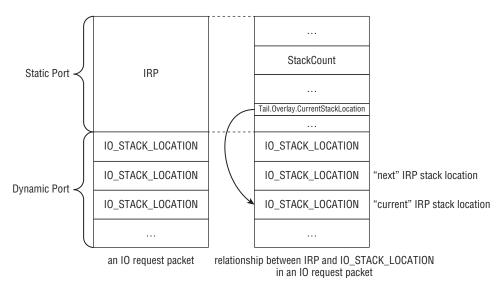

|           | I/O Request Packets                  | 144 |

|           | Structure of a Driver                | 146 |

|           | Entry Points                         | 147 |

|           | Driver and Device Objects            | 149 |

|           |                                                         | Contents | ххі |

|-----------|---------------------------------------------------------|----------|-----|

|           |                                                         |          |     |

|           | IRP Handling                                            | 150      |     |

|           | A Common Mechanism for User-Kernel Communication        | 150      |     |

|           | Miscellaneous System Mechanisms                         | 153      |     |

|           | Walk-Throughs                                           | 155      |     |

|           | An x86 Rootkit                                          | 156      |     |

|           | An x64 Rootkit                                          | 172      |     |

|           | Next Steps                                              | 178      |     |

|           | Exercises                                               | 180      |     |

|           | Building Confidence and Solidifying                     |          |     |

|           | Your Knowledge                                          | 180      |     |

|           | Investigating and Extending Your Knowledge              | 182      |     |

|           | Analysis of Real-Life Drivers                           | 184      |     |

| Chapter 4 | Debugging and Automation                                | 187      |     |

| Chapter 4 | The Debugging Tools and Basic Commands                  | 188      |     |

|           | Setting the Symbol Path                                 | 189      |     |

|           | Debugger Windows                                        | 189      |     |

|           |                                                         | 190      |     |

|           | Evaluating Expressions Process Control and Debut Events | 190      |     |

|           |                                                         |          |     |

|           | Registers, Memory, and Symbols                          | 198      |     |

|           | Breakpoints                                             | 208      |     |

|           | Inspecting Processes and Modules                        | 211      |     |

|           | Miscellaneous Commands                                  | 214      |     |

|           | Scripting with the Debugging Tools                      | 216      |     |

|           | Pseudo-Registers                                        | 216      |     |

|           | Aliases                                                 | 219      |     |

|           | Language                                                | 226      |     |

|           | Script Files                                            | 240      |     |

|           | Using Scripts Like Functions                            | 244      |     |

|           | Example Debug Scripts                                   | 249      |     |

|           | Using the SDK                                           | 257      |     |

|           | Concepts                                                | 258      |     |

|           | Writing Debugging Tools Extensions                      | 262      |     |

|           | Useful Extensions, Tools, and Resources                 | 264      |     |

| Chapter 5 | Obfuscation                                             | 267      |     |

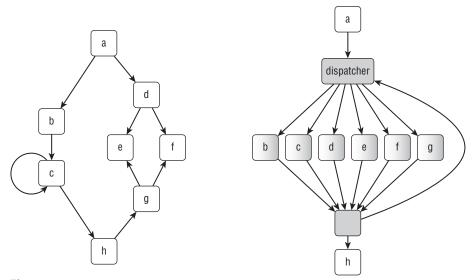

| •         | A Survey of Obfuscation Techniques                      | 269      |     |

|           | The Nature of Obfuscation: A Motivating Example         | 269      |     |

|           | Data-Based Obfuscations                                 | 273      |     |

|           | Control-Based Obfuscation                               | 278      |     |

|           | Simultaneous Control-Flow and Data-Flow                 |          |     |

|           | Obfuscation                                             | 284      |     |

|           | Achieving Security by Obscurity                         | 288      |     |

|           | A Survey of Deobfuscation Techniques                    | 289      |     |

|           | The Nature of Deobfuscation: Transformation Inversion   | 289      |     |

|           | Deobfuscation Tools                                     | 295      |     |

|           | Practical Deobfuscation                                 | 312      |     |

|           |                                                         |          |     |

# xxii Contents

| Index    |                                            | 343 |

|----------|--------------------------------------------|-----|

| Appendix | Sample Names and Corresponding SHA1 Hashes | 341 |

|          | Exercises                                  | 336 |

|          | Final Thoughts                             | 336 |

|          | Solving the Challenge                      | 334 |

|          | Symbolic Execution                         | 333 |

|          | Analyzing Handlers Semantics               | 330 |

|          | First Impressions                          | 328 |

|          | Case Study                                 | 328 |

# Introduction

The reverse engineering learning process is similar to that of foreign language acquisition for adults. The first phase of learning a foreign language begins with an introduction to letters in the alphabet, which are used to construct words with well-defined semantics. The next phase involves understanding the grammatical rules governing how words are glued together to produce a proper sentence. After being accustomed to these rules, one then learns how to stitch multiple sentences together to articulate complex thoughts. Eventually it reaches the point where the learner can read large books written in different styles and still understand the thoughts therein. At this point, one can read reference books on the more esoteric aspects of the language—historical syntax, phonology, and so on.

In reverse engineering, the language is the architecture and assembly language. A word is an assembly instruction. Paragraphs are sequences of assembly instructions. A book is a program. However, to fully understand a book, the reader needs to know more than just vocabulary and grammar. These additional elements include structure and style of prose, unwritten rules of writing, and others. Understanding computer programs also requires a mastery of concepts beyond assembly instructions.

It can be somewhat intimidating to start learning an entirely new technical subject from a book. However, we would be misleading you if we were to claim that reverse engineering is a simple learning endeavor and that it can be completely mastered by reading this book. The learning process is quite involved because it requires knowledge from several disparate domains of knowledge. For example, an effective reverse engineer needs to be knowledgeable in computer architecture, systems programming, operating systems, compilers, and so on; for certain areas, a strong mathematical background is necessary. So how do you

know where to start? The answer depends on your experience and skills. Because we cannot accommodate everyone's background, this introduction outlines the learning and reading methods for those without any programming background. You should find your "position" in the spectrum and start from there.

For the sake of discussion, we loosely define reverse engineering as the process of understanding a system. It is a problem-solving process. A system can be a hardware device, a software program, a physical or chemical process, and so on. For the purposes of the book, the system is a software program. To understand a program, you must first understand how software is written. Hence, the first requirement is knowing how to program a computer through a language such as C, C++, Java, and others. We suggest first learning C due to its simplicity, effectiveness, and ubiquity. Some excellent references to consider are *The C Programming Language*, by Brian Kernighan and Dennis Ritchie (Prentice Hall, 1988) and C: A Reference Manual, by Samuel Harbison (Prentice Hall, 2002). After becoming comfortable with writing, compiling, and debugging basic programs, consider reading Expert C Programming: Deep C Secrets, by Peter van der Linden (Prentice Hall, 1994). At this point, you should be familiar with high-level concepts such as variables, scopes, functions, pointers, conditionals, loops, call stacks, and libraries. Knowledge of data structures such as stacks, queues, linked lists, and trees might be useful, but they are not entirely necessary for now. To top it off, you might skim through Compilers: Principles, Techniques, and Tools, by Alfred Aho, Ravi Sethi, and Jeffrey Ullman, (Prentice Hall, 1994) and *Linkers and Loaders*, by John Levine (Morgan Kaufmann, 1999), to get a better understanding of how a program is really put together. The key purpose of reading these books is to gain exposure to basic concepts; you do not have to understand every page for now (there will be time for that later). Overachievers should consider Advanced Compiler Design and Implementation, by Steven Muchnick (Morgan Kaufmann, 1997).

Once you have a good understanding of how programs are generally written, executed, and debugged, you should begin to explore the program's execution environment, which includes the processor and operating system. We suggest first learning about the Intel processor by skimming through *Intel 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture* by Intel, with special attention to Chapters 2–7. These chapters explain the basic elements of a modern computer. Readers interested in ARM should consider *Cortex-A Series Programmer's Guide* and *ARM Architecture Reference Manual ARMv7-A and ARMv7-R Edition* by ARM. While our book covers x86/x64/ARM, we do not discuss every architectural detail. (We assume that the reader will refer to these manuals, as necessary.) In skimming through these manuals, you should have a basic appreciation of the technical building blocks of a computing system. For a more conceptual understanding, consider *Structured Computer Organization* by Andrew Tanenbaum (Prentice Hall, 1998). All readers should also consult the *Microsoft PE*

and COFF Specification. At this point, you will have all the necessary background to read and understand Chapter 1, "x86 and x64," and Chapter 2, "ARM."

Next, you should explore the operating system. There are many different operating systems, but they share many common concepts including processes, threads, virtual memory, privilege separation, multi-tasking, and so on. The best way to understand these concepts is to read *Modern Operating Systems*, by Andrew Tanenbaum (Prentice Hall, 2005). Although Tanenbaum's text is excellent for concepts, it does not discuss important technical details for real-life operating systems. For Windows, you should consider skimming through *Windows NT Device Driver Development*, by Peter Viscarola and Anthony Mason (New Riders Press, 1998); although it is a book on driver development, the background chapters provide an excellent and concrete introduction to Windows. (It is also excellent supplementary material for the Windows kernel chapter in this book.) For additional inspiration (and an excellent treatment of the Windows memory manager), you should also read *What Makes It Page? The Windows 7 (x64) Virtual Memory Manager*, by Enrico Martignetti (CreateSpace Independent Publishing Platform, 2012).

At this point, you would have all the necessary background to read and understand Chapter 3 "The Windows Kernel." You should also consider learning Win32 programming. *Windows System Programming*, by Johnson Hart (Addison-Wesley Professional, 2010), and *Windows via C/C++*, by Jeffrey Richter and Christophe Nasarre (Microsoft Press, 2007), are excellent references.

For Chapter 4, "Debugging and Automation," consider *Inside Windows Debugging: A Practical Guide to Debugging and Tracing Strategies in Windows*, by Tarik Soulami (Microsoft Press, 2012), and *Advanced Windows Debugging*, by Mario Hewardt and Daniel Pravat (Addison-Wesley Professional, 2007).

Chapter 5, "Obfuscation," requires a good understanding of assembly language and should be read after the x86/x64/ARM chapters. For background knowledge, consider *Surreptitious Software*: *Obfuscation, Watermarking, and Tamperproofing for Software Protection*, by Christian Collberg and Jasvir Nagra (Addison-Wesley Professional, 2009).

NOTE This book includes exercises and walk-throughs with real, malicious viruses and rootkits. We intentionally did this to ensure that readers can immediately apply their newly learned skills. The malware samples are referenced in alphabetical order (Sample A, B, C, ...), and you can find the corresponding SHA1 hashes in the Appendix. Because there may be legal concerns about distributing such samples with the book, we decided not to do so; however, you can download these samples by searching various malware repositories, such as www.malware.lu, or request them from the forums at http://kernelmode.info. Many of the samples are from famous hacking incidents that made worldwide news, so they should be interesting. Perhaps some enthusiastic readers will gather all the samples in a package and share them on BitTorrent.

If none of those options work for you, please feel free to email the authors. Make sure that you analyze these in a safe environment to prevent accidental self-infection.

In addition, to familiarize you with Metasm, we've prepared two exercise scripts: symbolic-execution-lvll.rb and symbolic-execution-lvl2.rb.

Answering the questions will lead you to a journey in Metasm internals. You can find the scripts at www.wiley.com/go/practicalreverseengineering.

It is important to realize that the exercises are a vital component of the book. The book was intentionally written in this way. If you simply read the book without doing the exercises, you will not understand or retain much. You should feel free to blog or write about your answers so that others can learn from them; you can post them on the Reverse Engineering reddit (www.reddit.com/r/ReverseEngineering) and get feedback from the community (and maybe the authors). If you successfully complete all of the exercises, pat yourself on the back and then send Bruce your resume.

The journey of becoming an effective reverse engineer is long and time consuming, requiring patience and endurance. You may fail many times along the way (by not understanding concepts or by failing to complete exercises in this book), but don't give up. Remember: Failing is part of success. With this guidance and the subsequent chapters, you should be well prepared for the learning journey.

We, the authors, would love to hear about your learning experience so that we can further adjust our material and improve the book. Your feedback will be invaluable to us and, potentially, future publications. You can send feedback and questions to Bruce Dang (bruce.dang@gmail.com), Alexandre Gazet (agazet@quarkslab.com), or Elias Bachaalany (elias.bachaalany@gmail.com).

T T x86 and x64

The x86 is little-endian architecture based on the Intel 8086 processor. For the purpose of our chapter, x86 is the 32-bit implementation of the Intel architecture (IA-32) as defined in the *Intel Software Development Manual*. Generally speaking, it can operate in two modes: *real* and *protected*. Real mode is the processor state when it is first powered on and only supports a 16-bit instruction set. Protected mode is the processor state supporting virtual memory, paging, and other features; it is the state in which modern operating systems execute. The 64-bit extension of the architecture is called x64 or x86-64. This chapter discusses the x86 architecture operating in protected mode.

x86 supports the concept of privilege separation through an abstraction called *ring level*. The processor supports four ring levels, numbered from 0 to 3. (Rings 1 and 2 are not commonly used so they are not discussed here.) Ring 0 is the highest privilege level and can modify all system settings. Ring 3 is the lowest privileged level and can only read/modify a subset of system settings. Hence, modern operating systems typically implement user/kernel privilege separation

by having user-mode applications run in ring 3, and the kernel in ring 0. The ring level is encoded in the cs register and sometimes referred to as the *current privilege level* (CPL) in official documentation.

This chapter discusses the x86/IA-32 architecture as defined in the *Intel 64* and IA-32 Architectures Software Developer's Manual, Volumes 1–3 (www.intel.com/content/www/us/en/processors/architectures-software-developer-manuals.html).

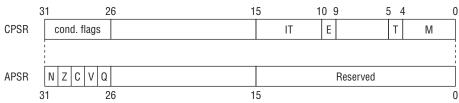

# **Register Set and Data Types**

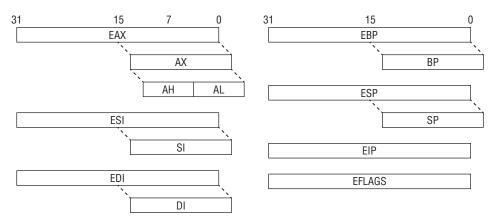

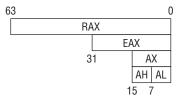

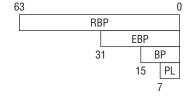

When operating in protected mode, the x86 architecture has eight 32-bit general-purpose registers (GPRs): EAX, EBX, ECX, EDX, EDI, ESI, EBP, and ESP. Some of them can be further divided into 8- and 16-bit registers. The instruction pointer is stored in the EIP register. The register set is illustrated in Figure 1-1. Table 1-1 describes some of these GPRs and how they are used.

Figure 1-1

**Table 1-1:** Some GPRs and Their Usage

| REGISTER | PURPOSE                                 |

|----------|-----------------------------------------|

| ECX      | Counter in loops                        |

| ESI      | Source in string/memory operations      |

| EDI      | Destination in string/memory operations |

| EBP      | Base frame pointer                      |

| ESP      | Stack pointer                           |

The common data types are as follows:

- Bytes—8 bits. Examples: AL, BL, CL

- Word—16 bits. Examples: AX, BX, CX

- Double word—32 bits. Examples: EAX, EBX, ECX

- Quad word—64 bits. While x86 does not have 64-bit GPRs, it can combine two registers, usually EDX: EAX, and treat them as 64-bit values in some scenarios. For example, the RDTSC instruction writes a 64-bit value to EDX: EAX.

The 32-bit EFLAGS register is used to store the status of arithmetic operations and other execution states (e.g., trap flag). For example, if the previous "add" operation resulted in a zero, the zF flag will be set to 1. The flags in EFLAGS are primarily used to implement conditional branching.

In addition to the GPRs, EIP, and EFLAGS, there are also registers that control important low-level system mechanisms such as virtual memory, interrupts, and debugging. For example, CRO controls whether paging is on or off, CR2 contains the linear address that caused a page fault, CR3 is the base address of a paging data structure, and CR4 controls the hardware virtualization settings. DRO-DR7 are used to set memory breakpoints. We will come back to these registers later in the "System Mechanism" section.

**NOTE** Although there are seven debug registers, the system allows only four memory breakpoints (DR0-DR3). The remaining registers are used for status.

There are also model-specific registers (MSRs). As the name implies, these registers may vary between different processors by Intel and AMD. Each MSR is identified by name and a 32-bit number, and read/written to through the RDMSR/WRMSR instructions. They are accessible only to code running in ring 0 and typically used to store special counters and implement low-level functionality. For example, the SYSENTER instruction transfers execution to the address stored in the IA32\_SYSENTER\_EIP MSR (0x176), which is usually the operating system's system call handler. MSRs are discussed throughout the book as they come up.

# **Instruction Set**

The x86 instruction set allows a high level of flexibility in terms of data movement between registers and memory. The movement can be classified into five general methods:

- Immediate to register

- Register to register

- Immediate to memory

- Register to memory and vice versa

- Memory to memory

The first four methods are supported by all modern architectures, but the last one is specific to x86. A classical RISC architecture like ARM can *only* read/write data from/to memory with load/store instructions (LDR and STR, respectively); for example, a simple operation like incrementing a value in memory requires three instructions:

- 1. Read the data from memory to a register (LDR).

- 2. Add one to the register (ADD).

- 3. Write the register to memory (STR).

On x86, such an operation would require only one instruction (either INC or ADD) because it can directly access memory. The MOVS instruction can read and write memory at the same time.

### **ARM**

; directly increment value at address EAX

Another important characteristic is that x86 uses variable-length instruction size: the instruction length can range from 1 to 15 bytes. On ARM, instructions are either 2 or 4 bytes in length.

# **Syntax**

Depending on the assembler/disassembler, there are two syntax notations for x86 assembly code, Intel and AT&T:

### Intel

```

mov ecx, AABBCCDDh

mov ecx, [eax]

mov ecx, eax

AT&T

movl $0xAABBCCDD, %ecx

movl (%eax), %ecx

movl %eax, %ecx

```

It is important to note that these are the same instructions but written differently. There are several differences between Intel and AT&T notation, but the most notable ones are as follows:

- AT&T prefixes the register with %, and immediates with \$. Intel does not do this.

- AT&T adds a prefix to the instruction to indicate operation width. For example, MOVL (long), MOVB (byte), etc. Intel does not do this.

- AT&T puts the source operand before the destination. Intel reverses the order.

Disassemblers/assemblers and other reverse-engineering tools (IDA Pro, OllyDbg, MASM, etc.) on Windows typically use Intel notation, whereas those on UNIX frequently follow AT&T notation (GCC). In practice, Intel notation is the dominant form and is used throughout this book.

## **Data Movement**

Instructions operate on values that come from registers or main memory. The most common instruction for moving data is MOV. The simplest usage is to move a register or immediate to register. For example:

```

01: BE 3F 00 0F 00 mov esi, 0F003Fh; set ESI = 0xF003

02: 8B F1 mov esi, ecx; set ESI = ECX

```

The next common usage is to move data to/from memory. Similar to other assembly language conventions, x86 uses square brackets ([]) to indicate memory access. (The only exception to this is the LEA instruction, which uses [] but does not actually reference memory.) Memory access can be specified in several different ways, so we will begin with the simplest case:

### Assembly

```

01: C7 00 01 00 00+ mov dword ptr [eax], 1; set the memory at address EAX to 1

02: 8B 08 mov ecx, [eax]; set ECX to the value at address EAX

03: 89 18 mov [eax], ebx; set the memory at address EAX to EBX

04: 89 46 34 mov [esi+34h], eax; set the memory address at (ESI+34) to EAX

05: 8B 46 34 mov eax, [esi+34h]; set EAX to the value at address (EAX+34)

06: 8B 14 01 mov edx, [ecx+eax]; set EDX to the value at address (ECX+EAX)

```

### Pseudo C

```

01: *eax = 1;

02: ecx = *eax;

03: *eax = ebx;

04: *(esi+34) = eax;

05: eax = *(esi+34);

06: edx = *(ecx+eax);

```

These examples demonstrate memory access through a base register and offset, where offset can be a register or immediate. This form is commonly used to access structure members or data buffers at a location computed at runtime. For example, suppose that ECX points to a structure of type KDPC with the layout

```

kd> dt nt!_KDPC

+0x000 Type : UChar

+0x001 Importance : UChar

+0x002 Number : Uint2B

+0x004 DpcListEntry : _LIST_ENTRY

+0x00c DeferredRoutine : Ptr32 void

+0x010 DeferredContext : Ptr32 Void

+0x014 SystemArgument1 : Ptr32 Void

+0x018 SystemArgument2 : Ptr32 Void

+0x01c DpcData : Ptr32 Void

```

and used in the following context:

### Assembly

```

01: 8B 45 0C mov eax, [ebp+0Ch]

02: 83 61 1C 00 and dword ptr [ecx+1Ch], 0

03: 89 41 0C mov [ecx+0Ch], eax

04: 8B 45 10 mov eax, [ebp+10h]

05: C7 01 13 01 00+ mov dword ptr [ecx], 113h

06: 89 41 10 mov [ecx+10h], eax

```

### Pseudo C

```

KDPC *p = ...;

p->DpcData = NULL;

p->DeferredRoutine = ...;

*(int *)p = 0x113;

p->DeferredContext = ...;

```

Line 1 reads a value from memory and stores it in EAX. The DeferredRoutine field is set to this value in line 3. Line 2 clears the DpcData field by AND'ing it

with 0. Line 4 reads another value from memory and stores it in EAX. The DeferredContext field is set to this value in line 6.

Line 5 writes the double-word value 0x113 to the base of the structure. Why does it write a double-word value at the base if the first field is only 1 byte in size? Wouldn't that implicitly set the Importance and Number fields as well? The answer is yes. Figure 1-2 shows the result of converting 0x113 to binary.

| 00000000 00000000 |            |          |  |  |

|-------------------|------------|----------|--|--|

| 00000000 00000000 | 00000001   | 00010011 |  |  |

| Number            | Importance | Туре     |  |  |

Figure 1-2

The Type field is set to 0x13 (bold bits), Importance is set to 0x1 (underlined bits), and Number is set to 0x0 (the remaining bits). By writing one value, the code managed to initialize three fields with a single instruction! The code could have been written as follows:

```

01: 8B 45 0C

mov

eax, [ebp+0Ch]

02: 83 61 1C 00

and dword ptr [ecx+1Ch], 0

03: 89 41 OC

mov [ecx+0Ch], eax

04: 8B 45 10

eax, [ebp+10h]

mov

05: C6 01 13

byte ptr [ecx],13h

mov

06: C6 41 01 01

mov

byte ptr [ecx+1],1

07: 66 C7 41 02 00+ mov

word ptr [ecx+2],0

08: 89 41 10

mov

[ecx+10h], eax

```

The compiler decided to fold three instructions into one because it knew the constants ahead of time and wants to save space. The three-instruction version occupies 13 bytes (the extra byte in line 7 is not shown), whereas the one-instruction version occupies 6 bytes. Another interesting observation is that memory access can be done at three granularity levels: byte (line 5–6), word (line 6), and double-word (line 1–4, 8). The default granularity is 4 bytes, which can be changed to 1 or 2 bytes with an override prefix. In the example, the override prefix bytes are C6 and 66 (italicized). Other prefixes are discussed as they come up.

The next memory access form is commonly used to access array-type objects. Generally, the format is as follows: [Base + Index \* scale]. This is best understood through examples:

```

01: 8B 34 B5 40 05+ mov esi, _KdLogBuffer[esi*4]

; always written as mov esi, [_KdLogBuffer + esi * 4]

; _KdLogBuffer is the base address of a global array and

; ESI is the index; we know that each element in the array

; is 4 bytes in length (hence the scaling factor)

```

```

02: 89 04 F7 mov [edi+esi*8], eax; here is EDI is the array base address; ESI is the array; index; element size is 8.

```

In practice, this is observed in code looping over an array. For example:

Line 2 reads a double-word from offset +4 from EDI and then uses it as the base address into an array in line 3; hence, you know that EDI is likely a structure that has an array at +4. Line 7 increments the index. Line 8 compares the index against a value at offset +0 in the same structure. Given this info, this small loop can be decompiled as follows:

The MOVSB/MOVSW/MOVSD instructions move data with 1-, 2-, or 4-byte granularity between two memory addresses. They implicitly use EDI/ESI as the destination/source address, respectively. In addition, they also automatically update the source/destination address depending on the direction flag (DF) flag in EFLAGS. If DF is 0, the addresses are decremented; otherwise, they are incremented. These instructions are typically used to implement string or memory copy functions when the length is known at compile time. In some cases, they are accompanied by the REP prefix, which repeats an instruction up to ECX times. Consider the following example:

#### Assembly

```

01: BE 28 B5 41 00 mov esi, offset _RamdiskBootDiskGuid

; ESI = pointer to RamdiskBootDiskGuid

02: 8D BD 40 FF FF+ lea edi, [ebp-0C0h]

; EDI is an address somewhere on the stack

03: A5

movsd

; copies 4 bytes from EDI to ESI; increment each by 4

movsd

; same as above

05: A5

movsd

; save as above

06: A5

movsd

; same as above

```

#### Pseudo C

```

/* a GUID is 16-byte structure */

GUID RamDiskBootDiskGuid = ...; // global

GUID foo;

memcpy(&foo, &RamdiskBootDiskGuid, sizeof(GUID));

```

Line 2 deserves some special attention. Although the LEA instruction uses [], it actually does not read from a memory address; it simply evaluates the expression in square brackets and puts the result in the destination register. For example, if EBP were 0x1000, then EDI would be 0xF40 (=0x1000 - 0xC0) after executing line 2. The point is that LEA does not access memory, despite the misleading syntax.

The following example, from nt!KiInitSystem, uses the REP prefix:

```

01: 6A 08

push

; push 8 on the stack (will explain stacks

; later)

02: ...

03: 59

pop ecx ; pop the stack. Basically sets ECX to 8.

04: ...

05: BE 00 44 61 00 mov esi, offset KeServiceDescriptorTable

06: BF C0 43 61 00 mov edi, offset KeServiceDescriptorTableShadow

07: F3 A5

rep movsd ; copy 32 bytes (movsd repeated 8 times)

; from this we can deduce that whatever these two objects are, they are

; likely to be 32 bytes in size.

```

The rough C equivalent of this would be as follows:

```

memcpy(&KeServiceDescriptorTableShadow, &KeServiceDescriptorTable, 32);

```

The final example, nt!MmInitializeProcessAddressSpace, uses a combination of these instructions because the copy size is not a multiple of 4:

```

01: 8D B0 70 01 00+ lea esi, [eax+170h]; EAX is likely the base address of a structure. Remember what we said; about LEA ...

02: 8D BB 70 01 00+ lea edi, [ebx+170h]; EBX is likely to be base address of another structure of the same type 03: A5 movsd

04: A5 movsd

05: A5 movsd

06: 66 A5 movsw

07: A4 movsb

```

After lines 1–2, you know that EAX and EBX are likely to be of the same type because they are being used as source/destination and the offset is identical. This code snippet simply copies 15 bytes from one structure field to another. Note that the code could also have been written using the MOVSB instruction with a REP prefix and ECX set to 15; however, that would be inefficient because it results in 15 reads instead of only five.

Another class of data movement instructions with implicit source and destination includes the SCAS and STOS instructions. Similar to MOVS, these instructions can operate at 1-, 2-, or 4-byte granularity. SCAS implicitly compares AL/AX/EAX with data starting at the memory address EDI; EDI is automatically incremented/decremented depending on the DF bit in EFLAGS. Given its semantic, SCAS is commonly used along with the REP prefix to find a byte, word, or double-word in a buffer. For example, the C strlen() function can be implemented as follows:

```

01: 30 C0

xor

al, al

; set AL to 0 (NUL byte). You will frequently observe the XOR reg, reg

; pattern in code.

02: 89 FB mov ebx, edi

; save the original pointer to the string

03: F2 AE

repne scasb

; repeatedly scan forward one byte at a time as long as AL does not match the

; byte at EDI when this instruction ends, it means we reached the NUL byte in

; the string buffer

sub

edi, ebx

; edi is now the NUL byte location. Subtract that from the original pointer

; to the length.

```

STOS is the same as SCAS except that it writes the value AL/AX/EAX to EDI. It is commonly used to initialize a buffer to a constant value (such as memset ()). Here is an example:

```

04: 8B FE mov edi, esi

; set the destination address

05: F3 AB rep stosd

; write 36 bytes of zero to the destination buffer (STOSD repeated 9 times)

; this is equivalent lent to memset(edi, 0, 36)

```

LODS is another instruction from the same family. It reads a 1-, 2-, or 4-byte value from ESI and stores it in AL, AX, or EAX.

# **Exercise**

1. This function uses a combination SCAS and STOS to do its work. First, explain what is the type of the [EBP+8] and [EBP+C] in line 1 and 8, respectively. Next, explain what this snippet does.

```

01: 8B 7D 08

mov edi, [ebp+8]

02: 8B D7

mov edx, edi

03: 33 C0

xor eax, eax

04: 83 C9 FF

or ecx, 0FFFFFFFh

05: F2 AE

repne scasb

add ecx, 2

06: 83 C1 02

neg ecx

mov al, [ebp+0Ch]

mov edi, edx

07: F7 D9

08: 8A 45 0C

09: 8B FA

rep stosb

10: F3 AA

11: 8B C2

mov eax, edx

```

# **Arithmetic Operations**

Fundamental arithmetic operations such as addition, subtraction, multiplication, and division are natively supported by the instruction set. Bit-level operations such as AND, OR, XOR, NOT, and left and right shift also have native corresponding instructions. With the exception of multiplication and division, the remaining instructions are straightforward in terms of usage. These operations are explained with the following examples:

```

01: 83 C4 14

add esp, 14h

; esp = esp + 0x14

02: 2B C8

sub ecx, eax

; ecx = ecx - eax

03: 83 EC 0C

sub esp, 0Ch

; esp = esp - 0xC

04: 41

inc ecx

; ecx = ecx + 1

05: 4F

dec edi

; edi = edi - 1

06: 83 C8 FF

07: 83 E1 07

08: 33 CO

not edi

shl cl, 4

09: F7 D7

; edi = ~edi

10: C0 E1 04

; cl = cl << 4

shr ecx, 1

rol al, 3

ror al, 1

11: D1 E9

; ecx = ecx >> 1

12: C0 C0 03

; rotate AL left 3 positions

13: D0 C8

; rotate AL right 1 position

```

The left and right shift instructions (lines 11–12) merit some explanation, as they are frequently observed in real-life code. These instructions are typically used to optimize multiplication and division operations where the multiplicand and divisor are a power of two. This type of optimization is sometimes known as *strength reduction* because it replaces a computationally expensive operation with a cheaper one. For example, integer division is relatively a slow operation, but when the divisor is a power of two, it can be reduced to shifting bits to the right; 100/2 is the same as 100>>1. Similarly, multiplication by a power of two can be reduced to shifting bits to the left; 100\*2 is the same as 100<<1.

Unsigned and signed multiplication is done through the MUL and IMUL instructions, respectively. The MUL instruction has the following general form: MUL reg/memory. That is, it can only operate on register or memory values. The register is multiplied with AL, AX, or EAX and the result is stored in AX, DX:AX, or EDX:EAX, depending on the operand width. For example:

```

01: F7 E1 mul ecx ; EDX:EAX = EAX * ECX

02: F7 66 04 mul dword ptr [esi+4] ; EDX:EAX = EAX * dword_at(ESI+4)

03: F6 E1 mul cl ; AX = AL * CL

04: 66 F7 E2 mul dx ; DX:AX = AX * DX

```

## Consider a few other concrete examples:

```

01: B8 03 00 00 00 mov eax,3 ; set EAX=3

02: B9 22 22 22 22 mov ecx,22222222h ; set ECX=0x222222222

03: F7 E1 mul ecx ; EDX:EAX = 3 * 0x22222222 = ; 0x66666666

04: B8 03 00 00 00 mov eax,3 ; set EAX=3

05: B9 00 00 00 80 mov ecx,80000000h ; set ECX=0x80000000

06: F7 E1 mul ecx ; EDX:EAX = 3 * 0x80000000 = ; 0x180000000

06: F7 E1 mul ecx ; EDX:EAX = 3 * 0x80000000 = ; 0x180000000 ; hence, EDX=1, EAX=0x80000000

```

The reason why the result is stored in EDX: EAX for 32-bit multiplication is because the result potentially may not fit in one 32-bit register (as demonstrated in lines 4–6).

IMUL has three forms:

- IMUL reg/mem Same as MUL

- IMUL reg1, reg2/mem reg1 = reg1 \* reg2/mem

- IMUL reg1, reg2/mem, imm reg1 = reg2 \* imm

Some disassemblers shorten the parameters. For example:

```

01: F7 E9 imul ecx ; EDX:EAX = EAX * ECX 02: 69 F6 A0 01 00+ imul esi, 1A0h ; ESI = ESI * 0x1A0

```

```

03: OF AF CE imul ecx, esi ; ECX = ECX * ESI

```

Unsigned and signed division is done through the DIV and IDIV instructions, respectively. They take only one parameter (divisor) and have the following form: DIV/IDIV reg/mem. Depending on the divisor's size, DIV will use either AX, DX:AX, or EDX:EAX as the dividend, and the resulting quotient/remainder pair are stored in AL/AH, AX/DX, or EAX/EDX. For example:

# **Stack Operations and Function Invocation**

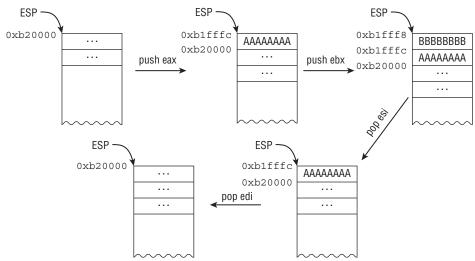

The stack is a fundamental data structure in programming languages and operating systems. For example, local variables in C are stored on the functions' stack space. When the operating system transitions from ring 3 to ring 0, it saves state information on the stack. Conceptually, a stack is a last-in first-out data structure supporting two operations: push and pop. Push means to put something on top of the stack; pop means to remove an item from the top. Concretely speaking, on x86, a stack is a contiguous memory region pointed to by ESP and it grows downwards. Push/pop operations are done through the PUSH/POP instructions and they implicitly modify ESP. The PUSH instruction decrements ESP and then writes data at the location pointed to by ESP; POP reads the data and increments ESP. The default auto-increment/decrement value is 4, but it can be changed to 1 or 2 with a prefix override. In practice, the value is almost always 4 because the OS requires the stack to be double-word aligned.

Suppose that ESP initially points to 0xb20000 and you have the following code:

```

; initial ESP = 0xb20000

01: B8 AA AA AA AA mov eax,0AAAAAAAA

02: BB BB BB BB mov ebx,0BBBBBBBBh

03: B9 CC CC CC CC mov ecx,0CCCCCCCh

04: BA DD DD DD mov edx,0DDDDDDDh

05: 50 push eax

; address 0xb1fffc will contain the value 0xAAAAAAAA and ESP

; will be 0xb1fffc (=0xb20000-4)

```

```

06: 53 push ebx

; address 0xb1fff8 will contain the value 0xBBBBBBBB and ESP

; will be 0xb1fff8 (=0xb1fffc-4)

07: 5E pop esi

; ESI will contain the value 0xBBBBBBBB and ESP will be 0xb1fffc

; (=0xb1fff8+4)

08: 5F pop edi

; EDI will contain the value 0xAAAAAAAA and ESP will be 0xb20000

; (=0xb1fffc+4)

```

Figure 1-3 illustrates the stack layout.

Figure 1-3

ESP can also be directly modified by other instructions, such as ADD and SUB. While high-level programming languages have the concept of functions that can be called and returned from, the processor does not provide such abstraction. At the lowest level, the processor operates only on concrete objects, such as registers or data coming from memory. How are functions translated at the machine level? They are implemented through the stack data structure! Consider the following function:

#### C

```

int

__cdecl addme(short a, short b)

{

return a+b;

}

```

#### Assembly

```

01: 004113A0 55 push ebp

```

```

02: 004113A1 8B EC mov ebp, esp

03: ...

04: 004113BE 0F BF 45 08 movsx eax, word ptr [ebp+8]

05: 004113C2 0F BF 4D 0C movsx ecx, word ptr [ebp+0Ch]

06: 004113C6 03 C1 add eax, ecx

07: ...

08: 004113CB 8B E5 mov esp, ebp

09: 004113CD 5D pop ebp

10: 004113CE C3 retn

```

The function is invoked with the following code:

C

```

sum = addme(x, y);

```

#### Assembly

```

01: 004129F3 50 push eax

02: ...

03: 004129F8 51 push ecx

04: 004129F9 E8 F1 E7 FF FF call addme

05: 004129FE 83 C4 08 add esp, 8

```

Before going into the details, first consider the CALL/RET instructions and calling conventions. The CALL instruction performs two operations:

- 1. It pushes the return address (address immediately after the CALL instruction) on the stack.

- 2. It changes EIP to the call destination. This effectively transfers control to the call target and begins execution there.

RET simply pops the address stored on the top of the stack into EIP and transfers control to it (literally like a "POP EIP" but such instruction sequence does not exist on x86). For example, if you want to begin execution at 0x12345678, you can just do the following:

```

01: 68 78 56 34 12 push 0x12345678

02: C3 ret

```

A *calling convention* is a set of rules dictating how function calls work at the machine level. It is defined by the Application Binary Interface (ABI) for a particular system. For example, should the parameters be passed through the stack, in registers, or both? Should the parameters be passed in from left-to-right or right-to-left? Should the return value be stored on the stack, in registers, or both? There are many calling conventions, but the popular ones are CDECL, STDCALL, THISCALL, and FASTCALL. (The compiler can also generate its own custom calling convention, but those will not be discussed here.) Table 1-2 summarizes their semantic.

Table 1-2: Calling Conventions

|                        | CDECL                                                                                  | STDCALL                                                    | FASTCALL                                                                   |

|------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------|

| Parameters             | Pushed on the stack from right-to-left. Caller must clean up the stack after the call. | Same as CDECL except that the callee must clean the stack. | First two parameters are passed in ECX and EDX. The rest are on the stack. |

| Return value           | Stored in EAX.                                                                         | Stored in EAX.                                             | Stored in EAX.                                                             |

| Non-volatile registers | EBP, ESP, EBX,<br>ESI, EDI.                                                            | EBP, ESP, EBX,<br>ESI, EDI.                                | EBP, ESP, EBX, ESI, EDI.                                                   |

We now return to the code snippet to discuss how the function addme is invoked. In line 1 and 3, the two parameters are pushed on the stack; ECX and EAX are the first and second parameter, respectively. Line 4 invokes the addme function with the CALL instruction. This immediately pushes the return address, 0x4129FE, on the stack and begins execution at 0x4113A0. Figure 1-4 illustrates the stack layout after line 4 is executed.

Figure 1-4

After line 4 executes, we are now in the addme function body. Line 1 pushes EBP on the stack. Line 2 sets EBP to the current stack pointer. This two-instruction sequence is typically known as the *function prologue* because it establishes a new function frame. Line 4 reads the value at address EBP+8, which is the first parameter on the stack; line 5 reads the second parameter. Note that the parameters are accessed using EBP as the base register. When used in this context, EBP is known as the *base frame pointer* (see line 2) because it points to the stack frame for the current function, and parameters/locals can be accessed relative to it. The compiler can also be instructed to generate code that does not use EBP as the base frame pointer through an optimization called *frame pointer omission*. With such optimization, access to local variables and parameters is done relative to ESP, and EBP can be used as a general register like EAX, EBX, ECX, and so on. Line 6 adds the numbers and saves the result in EAX. Line 8 sets the stack pointer to the base frame pointer. Line 9 pops the saved EBP from line 1 into

EBP. This two-instruction sequence is commonly referred to as the *function epilogue* because it is at the end of the function and restores the previous function frame. At this point, the top of the stack contains the return address saved by the CALL instruction at 0x4129F9. Line 10 performs a RET, which pops the stack and resumes execution at 0x4129FE. Line 5 in the snippet shrinks the stack by 8 because the caller must clean up the stack per CDECL's calling convention.

If the function addme had local variables, the code would need to grow the stack by subtracting ESP after line 2. All local variables would then be accessible through a negative offset from EBP.

## **Exercises**

- 1. Given what you learned about CALL and RET, explain how you would read the value of EIP? Why can't you just do MOV EAX, EIP?

- 2. Come up with at least two code sequences to set EIP to 0xAABBCCDD.

- 3. In the example function, addme, what would happen if the stack pointer were not properly restored before executing RET?

- 4. In all of the calling conventions explained, the return value is stored in a 32-bit register (EAX). What happens when the return value does not fit in a 32-bit register? Write a program to experiment and evaluate your answer. Does the mechanism change from compiler to compiler?

# **Control Flow**

This section describes how the system implements conditional execution for higher-level constructs like if/else, switch/case, and while/for. All of these are implemented through the CMP, TEST, JMP, and Jcc instructions and EFLAGS register. The following list summarizes the common flags in EFLAGS:

- **ZF/Zero flag**—Set if the result of the previous arithmetic operation is zero.

- SF/Sign flag—Set to the most significant bit of the result.

- **CF/Carry flag**—Set when the result requires a carry. It applies to unsigned numbers.

- **OF/Overflow flag**—Set if the result overflows the max size. It applies to signed numbers.

Arithmetic instructions update these flags based on the result. For example, the instruction SUB EAX, EAX would cause ZF to be set. The Jcc instructions, where "cc" is a conditional code, changes control flow depending on these

flags. There can be up to 16 conditional codes, but the most common ones are described in Table 1-3.

Table 1-3: Common Conditional Codes

| CONDITIONAL CODE | ENGLISH DESCRIPTION                                              | MACHINE<br>DESCRIPTION        |

|------------------|------------------------------------------------------------------|-------------------------------|

| B/NAE            | Below/Neither Above nor Equal. Used for unsigned operations.     | CF=1                          |

| NB/AE            | Not Below/Above or Equal. Used for unsigned operations.          | CF=0                          |

| E/Z              | Equal/Zero                                                       | ZF=1                          |

| NE/NZ            | Not Equal/Not Zero                                               | ZF=0                          |

| L                | Less than/Neither Greater nor Equal. Used for signed operations. | (SF ^ OF) = 1                 |

| GE/NL            | Greater or Equal/Not Less than. Used for signed operations.      | $(SF \land OF) = 0$           |

| G/NLE            | Greater/Not Less nor Equal. Used for signed operations.          | $((SF \land OF) \mid ZF) = 0$ |

Because assembly language does not have a defined type system, one of the few ways to recognize signed/unsigned types is through these conditional codes.

The CMP instruction compares two operands and sets the appropriate conditional code in EFLAGS; it compares two numbers by subtracting one from another without updating the result. The TEST instruction does the same thing except it performs a logical AND between the two operands.

#### If-Else

If-else constructs are quite simple to recognize because they involve a compare/test followed by a Jcc. For example:

#### Assembly

```

01: mov esi, [ebp+8]

02: mov edx, [esi]

03: test edx, edx

04: jz short loc_4E31F9

05: mov ecx, offset _FsRtlFastMutexLookasideList

06: call _ExFreeToNPagedLookasideList@8

07: and dword ptr [esi], 0

08: lea eax, [esi+4]

09: push eax

10: call _FsRtlUninitializeBaseMcb@4

11: loc_4E31F9:

```

```

12:    pop    esi

13:    pop    ebp

14:    retn    4

15:    FsRtlUninitializeLargeMcb@4 endp

```

#### Pseudo C

```

if (*esi == 0) {

return;

}

ExFreeToNPagedLookasideList(...);

*esi = 0;

...

return;

OR

if (*esi != 0) {

...

ExFreeToNPagedLookasideList(...);

*esi = 0;

...

}

return;

```

Line 2 reads a value at location ESI and stores it in EDX. Line 3 ANDS EDX with itself and sets the appropriate flags in EFLAGS. Note that this pattern is commonly used to determine whether a register is zero. Line 4 jumps to loc\_4E31F9 (line 12) if ZF=1. If ZF=0, then it executes line 5 and continues until the function returns.

Note that there are two slightly different but logically equivalent C translations for this snippet.

#### Switch-Case

A switch-case block is a sequence of if/else statements. For example:

#### Switch-Case

```

switch(ch) {

case 'c':

handle_C();

break;

case 'h':

handle_H();

break;

default:

break;

}

domore();

...

```

#### If-Else

```

if (ch == 'c') {

handle_C();

} else

if (ch == 'h') {

handle_H();

}

domore();

```

Hence, the machine code translation will be a series if/else. The following simple example illustrates the idea:

#### Assembly

C

```

01:

push

ebp

02:

mov

ebp, esp

03:

mov eax, [ebp+8]

04:

sub eax, 41h

05:

jz

short loc_caseA

06: dec

eax

07:

jz short loc_caseB

08: dec

eax

09: jz

short loc_caseC

al, 5Ah

10:

mov

movzx eax, al

11:

12:

pop

ebp

13:

retn

14: loc_caseC:

15:

mov

al, 43h

16:

movzx eax, al

17: pop

ebp

18:

retn

19: loc caseB:

20:

mov

al, 42h

21: movzx eax, al

22: pop

ebp

23: retn

24: loc caseA:

25: mov

al, 41h

26: movzx eax, al

27: pop

ebp

28: retn

unsigned char switchme(int a)

unsigned char res;

```

```

switch(a) {

case 0x41:

res = 'A';

break;

case 0x42:

res = 'B';

break;

case 0x43:

res = 'C';

break;

default:

res = 'Z';

break;

}

return res;

}

```

Real-life switch-case statements can be more complex, and compilers commonly build a *jump table* to reduce the number of comparisons and conditional jumps. The jump table is essentially an array of addresses, each pointing to the handler for a specific case. This pattern can be observed in Sample J in sub\_10001110:

#### Assembly

```

01: cmp edi, 5

02: ja short loc_10001141

03: jmp ds:off_100011A4[edi*4]

04: loc 10001125:

05: mov esi, 40h

06: jmp short loc 10001145

07: loc 1000112C:

08: mov esi, 20h

short loc 10001145

09: jmp

10: loc 10001133:

11: mov esi, 38h

short loc_10001145

12: jmp

13: loc 1000113A:

14: mov esi, 30h

15: jmp short loc 10001145

16: loc 10001141:

17: mov esi, [esp+0Ch]

19: off 100011A4 dd offset loc 10001125

20: dd offset loc_10001125

21: dd offset loc 1000113A

22: dd offset loc 1000112C

23: dd offset loc 10001133

24: dd offset loc_1000113A

```

#### Pseudo C

```

switch(edi) {

case 0:

case 1:

// goto loc_10001125;

esi = 0x40;

break:

case 2:

case 5:

// goto loc 1000113A;

esi = 0x30;

break;

// goto loc_1000112C;

esi = 0x20;

break;

case 4:

// goto loc_10001133;

esi = 0x38;

break;

default:

// goto loc 10001141;

esi = *(esp+0xC)

break;

```

Here, the compiler knows that there are only five cases and the case value is consecutive; hence, it can construct the jump table and index into it directly (line 3). Without the jump table, there would be 10 additional instructions to test each case and branch to the handler. (There are other forms of switch/case optimizations, but we will not cover them here.)

# Loops

At the machine level, loops are implemented using a combination of Jcc and JMP instructions. In other words, they are implemented using if/else and goto constructs. The best way to understand this is to rewrite a loop using only if/else and goto. Consider the following example:

#### **Using for**

```

for (int i=0; i<10; i++) {

printf("%d\n", i);

}

printf("done!\n");</pre>

```

#### Using if/else and goto

```

int i = 0;

loop_start:

if (i < 10) {

printf("%d\n", i);

i++;

goto loop_start;

}

printf("done!n");</pre>

```

When compiled, both versions are identical at the machine-code level:

```

01: 00401002 mov

edi, ds: imp printf

02: 00401008 xor esi, esi

03: 0040100A lea ebx, [ebx+0]

04: 00401010 loc 401010:

05: 00401010 push

esi

; "%d\n"

06: 00401011 push offset Format

07: 00401016 call edi; imp printf

08: 00401018 inc esi

09: 00401019 add esp, 8

10: 0040101C cmp esi, 0Ah

11: 0040101F jl short loc 401010

12: 00401021 push offset aDone

; "done!\n"

13: 00401026 call edi; imp printf

14: 00401028

add

esp, 4

```

Line 1 sets EDI to the printf function. Line 2 sets ESI to 0. Line 4 begins the loop; however, note that it does not begin with a comparison. There is no comparison here because the compiler knows that the counter was initialized to 0 (see line 2) and is obviously going to be less than 10 so it skips the check. Lines 5–7 call the printf function with the right parameters (format specifier and our number). Line 8 increments the number. Line 9 cleans up the stack because printf uses the CDECL calling convention. Line 10 checks to see if the counter is less than 0xA. If it is, it jumps back to loc\_401010. If the counter is not less than 0xA, it continues execution at line 12 and finishes with a printf.

One important observation to make is that the disassembly allowed us to infer that the counter is a signed integer. Line 11 uses the "less than" conditional code (JL), so we immediately know that the comparison was done on signed integers. Remember: If "above/below," it is unsigned; if "less than/greater than," it is signed. Sample L has a small function, sub\_1000AE3B, with the following interesting loop:

#### Assembly

```

01: sub_1000AE3B proc near

02: push edi

```

```

03:

push

esi

04:

call ds:lstrlenA

05: mov

edi, eax

06: xor

ecx, ecx

07: xor

edx, edx

08: test edi, edi

09: jle

short loc 1000AE5B

10: loc 1000AE4D:

al, [edx+esi]

12:

mov

[ecx+esi], al

13: add

edx, 3

14: inc

ecx

15: cmp

edx, edi

16: jl

short loc 1000AE4D

17: loc 1000AE5B:

byte ptr [ecx+esi], 0

18:

mov

19: mov

eax, esi

20: pop

edi

21: retn

22: sub_1000AE3B endp

C

char *sub 1000AE3B (char *str)

int len, i=0, j=0;

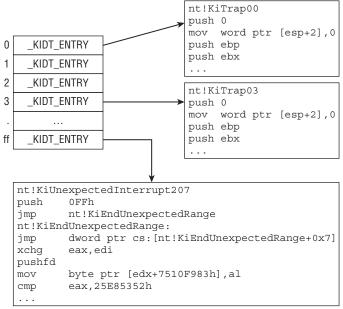

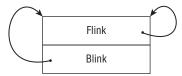

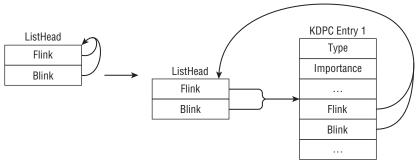

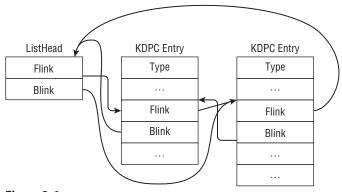

len = lstrlenA(str);